第一代 SmartSSD 技术交互式调研报告

由三星 Samsung 和赛灵思 Xilinx 合作的第一代 SmartSSD 是一款集成了 FPGA 计算功能的固态硬盘,旨在通过将数据处理任务从主 CPU 卸载到存储设备本身,来减少数据移动并加速特定应用的工作负载。

为何选择 SmartSSD?

数据路径对比分析

打破数据移动瓶颈,将计算推向数据源头,释放前所未有的应用性能。

点击按钮,直观感受数据流在不同架构下的差异。

核心技术优势

- 线性扩展: 性能随驱动器数量成比例增长,规避主机总线瓶颈。

- 高度灵活: 支持从 C++/OpenCL 到 RTL 的全栈开发,完全可定制。

- 降本增效: 显著降低延迟、功耗与 TCO,释放主机 CPU 资源。

实际应用性能表现

探索 SmartSSD 在关键应用领域的惊人表现。点击下方卡片查看详情。

工作原理

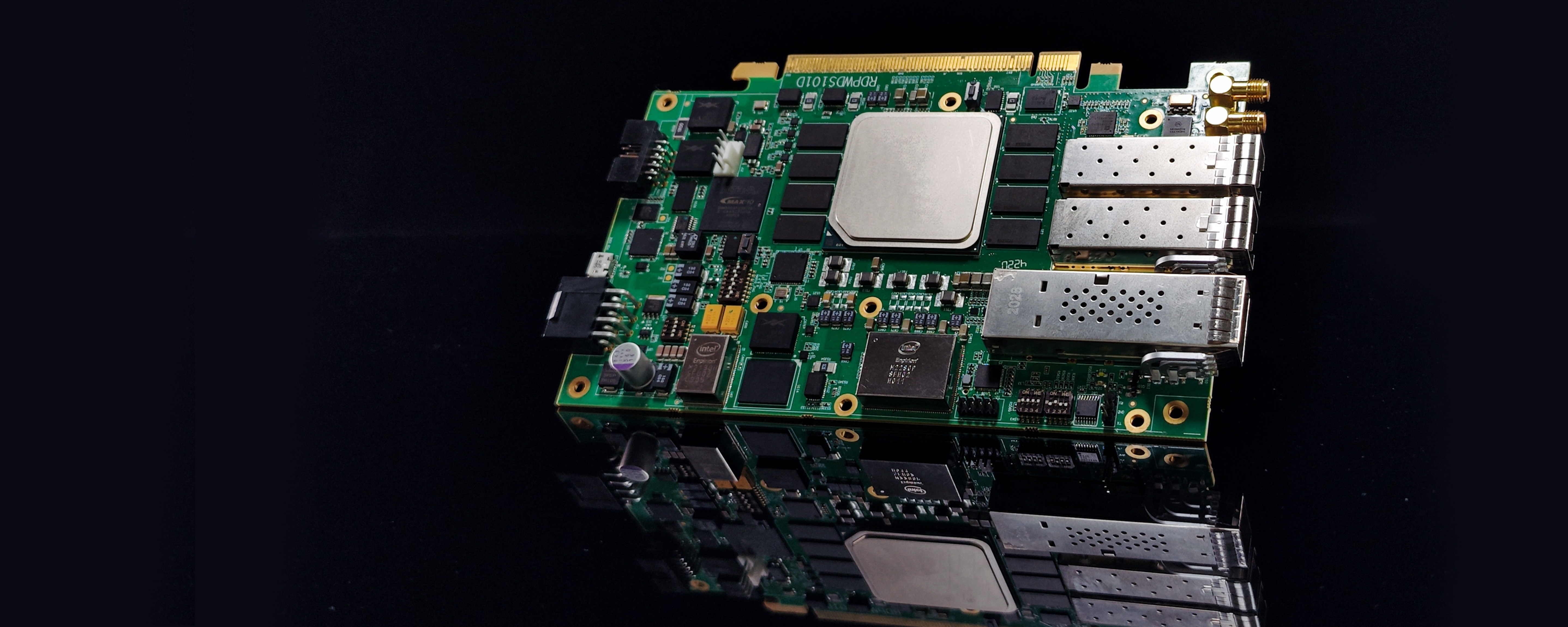

硬件架构组成

深入了解构成 SmartSSD 的硬件核心,探索其实现计算存储的精妙设计。

AMD Kintex UltraScale+ FPGA

FPGA-SSD 直连,绕过主机

三星高性能 V-NAND SSD

关键技术规格

| 类别 | 规格项 | 参数 |

|---|---|---|

| 存储 | 容量 | 3.84 TB |

| 顺序读/写 | 高达 3,300 / 2,000 MB/s | |

| 加速器 | FPGA 型号 | AMD Kintex UltraScale+ KU15P |

| 逻辑资源 | 114.3 万系统逻辑单元 (~30 万可用 LUTs) | |

| 片上内存 | 36.0 Mbit UltraRAM + 34.6 Mbit 分布式 RAM | |

| 计算单元 | 1,968 DSP 切片 | |

| 专用 DRAM | 4 GB DDR4 |

开始开发

开发环境准备

这里梳理了两条核心开发路径。选择适合您的技术栈,开启您的 SmartSSD 之旅。

此路径将 FPGA 开发抽象为软件模式,适合希望快速原型和迭代的软件工程师。

使用 C++ 和 XRT API 编写主机应用,控制数据流;使用 C++/OpenCL 和 HLS Pragma 编写将在 FPGA 上执行的内核函数。

将每个内核的源文件编译为 Xilinx 对象文件 (.xo),这是硬件描述的中间形态。

将一个或多个 .xo 文件与目标平台链接,生成包含最终硬件电路的二进制文件 (.xclbin)。

将 .xclbin 和主机可执行文件打包,支持软件仿真、硬件仿真和最终的硬件部署。

学习资源

官方示例与社区项目

从官方示例到社区项目,我们为您精选了加速学习进程的核心资源。

性能分析与优化

Vitis 分析器应用实践

学习使用 Vitis Analyzer,像专家一样定位性能瓶颈,验证您的设计是否充分发挥了 SmartSSD 的架构优势。

将鼠标悬停在时间轴的事件上,可以查看详细信息。这个交互式视图模仿了 Vitis 分析器中的真实追踪数据,帮助你理解 SmartSSD 操作的并行性和时序。