在 VSCode 中配置 Verilog 插件

前言

Visual Studio Code(VSCode)作为当今最受欢迎的代码编辑器之一,凭借其丰富的插件生态系统和强大的扩展能力,已经成为众多开发者的首选工具。对于 FPGA 开发者而言,传统的 Verilog 开发往往依赖于厂商提供的 IDE,如 Xilinx 的 Vivado 或 Intel 的 Quartus,虽然功能强大,但在代码编辑体验上往往不如专业的代码编辑器。

本文主要针对使用 Vivado 搭配 Verilog 开发的场景,通过配置相关插件和环境,让你能够在 VSCode 中享受现代化的代码编辑体验,同时保持与 Vivado 工具链的无缝集成。从基础的语法高亮、代码检查,到智能补全和 AI 辅助编程,这些配置将显著提升你的 FPGA 开发效率。

核心插件配置

插件概览

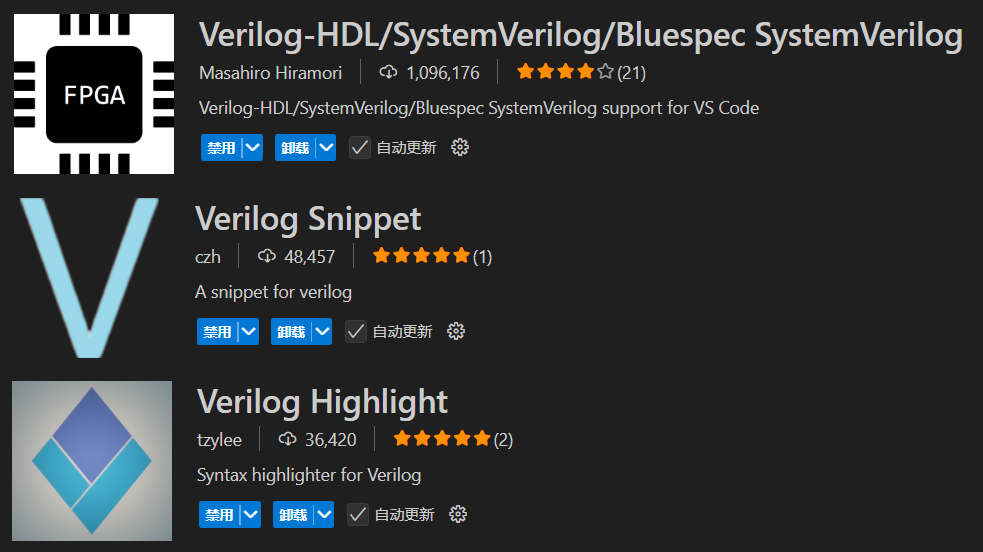

在 VSCode 中开发 Verilog,我们需要三个核心插件来提供完整的开发体验:

- Verilog-HDL/SystemVerilog/Bluespec SystemVerilog:提供语法高亮、代码检查和基础自动补全功能的综合性插件

- Verilog Snippet:增强代码片段和自动补全功能

- Verilog Highlight:优化语法高亮显示效果

这三个插件分别针对代码检查、自动补全以及语法高亮等不同方面进行优化。值得注意的是,Verilog-HDL/SystemVerilog/Bluespec SystemVerilog 插件本身是一款综合类型的插件,已经包含了自动补全和语法高亮功能,而 Verilog Snippet 和 Verilog Highlight 是在此基础上的补充和优化。

快速配置指南

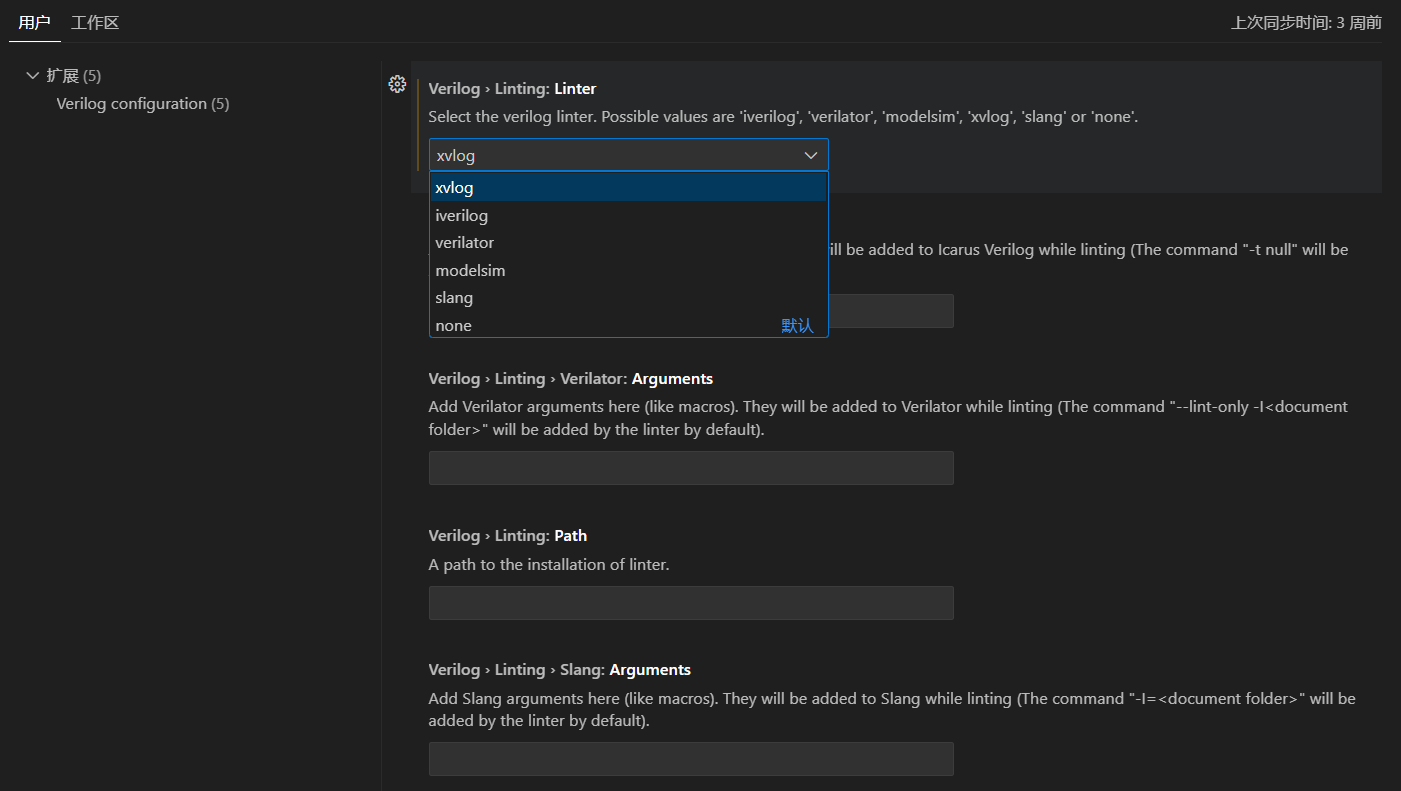

在确保你已经安装完成 Vivado 的前提下,我们需要对 Verilog-HDL/SystemVerilog/Bluespec SystemVerilog 插件的代码检查功能进行配置,使用 Vivado 的 xvlog 作为 Linter。

配置步骤如下:

- 打开 VSCode 设置(

Ctrl+,) - 搜索 “verilog linter”

- 将 Linter 设置为 “xvlog”

- 确保 Vivado 的安装路径已添加到系统环境变量中

完成上述插件的下载和快速配置后,你就可以优雅地使用 VSCode 来编写 Verilog 代码了。此时,VSCode 将能够实时检测代码中的语法错误和警告,为你提供专业级的代码编辑体验。

高级功能配置

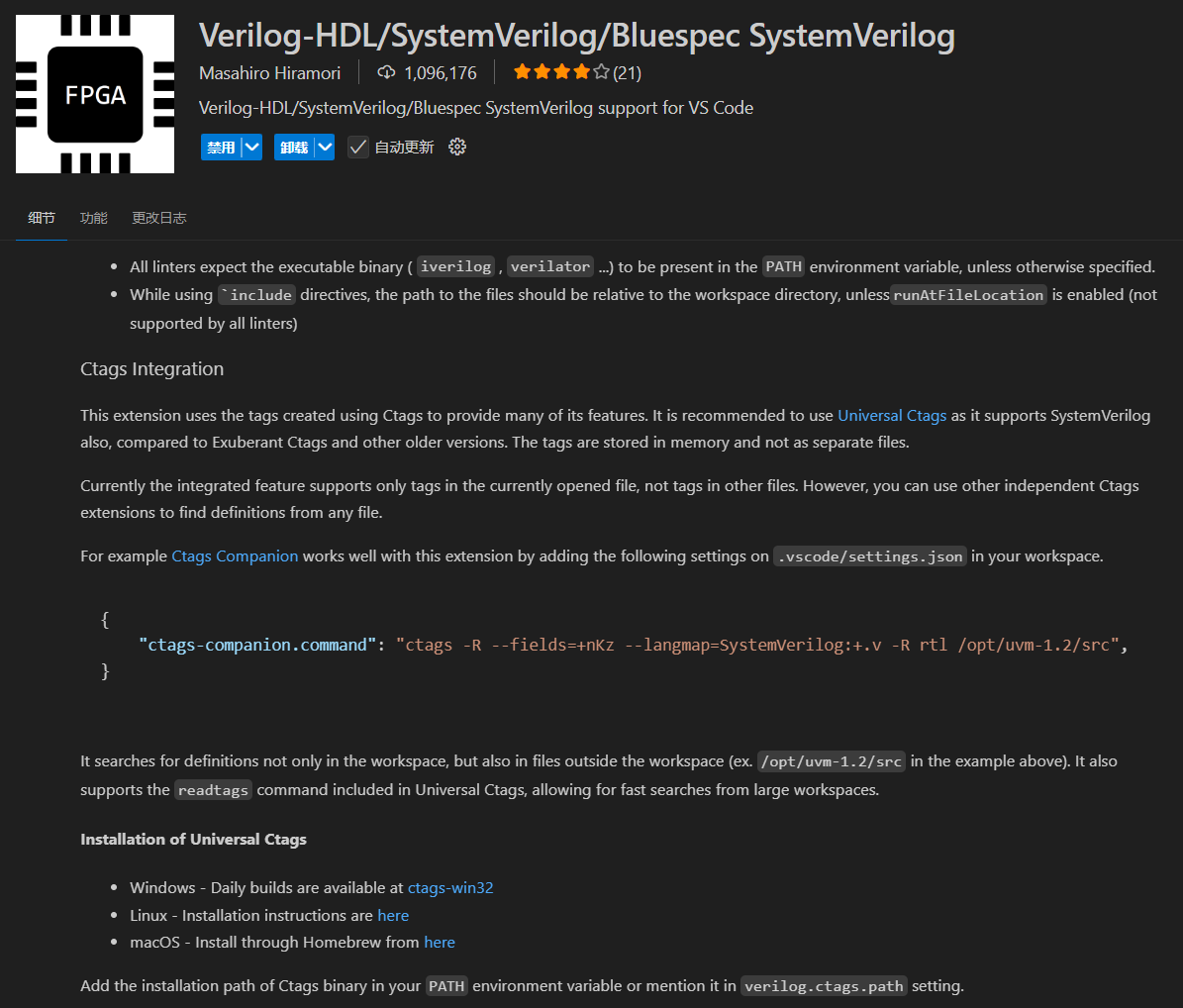

如果你希望获得更强大的自动补全功能,可以通过配置 ctags 来增强 Verilog-HDL/SystemVerilog/Bluespec SystemVerilog 插件的能力。

ctags 配置能够提供:

- 更准确的模块名补全

- 函数和任务的智能提示

- 跨文件的符号跳转功能

- 更好的代码导航体验

与 Vivado 的集成配置

设置 VSCode 为默认编辑器

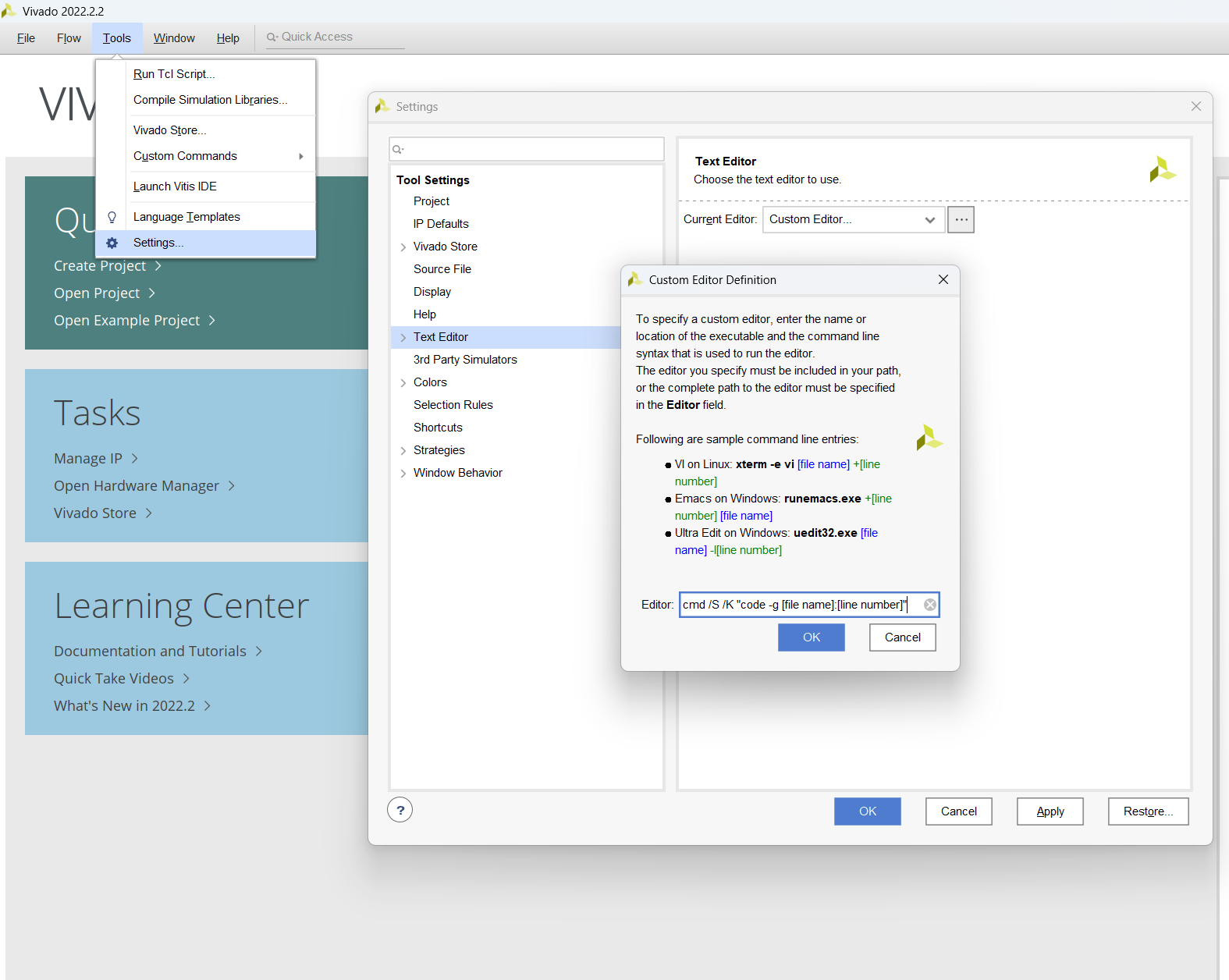

为了实现 Vivado 与 VSCode 的无缝集成,我们可以将 VSCode 设置为 Vivado 的默认文本编辑器。这样在 Vivado 中双击文件或查看错误时,就会自动在 VSCode 中打开对应的文件和行号。

配置方法:

- 在 Vivado 中打开

Tools → Settings → General → Text Editor - 在 Custom Editor 字段中输入:

cmd /S /K "code -g [file name]:[line number]" - 点击 OK 保存设置

注意事项:

- 对于 Vivado 2024 及更高版本,Current Editor 选项中已经内置了 VSCode 选项

- 即使使用 Custom Editor 配置,也不会影响 Vivado 正确调用 VSCode

- 确保 VSCode 的

code命令已添加到系统 PATH 环境变量中

AI 辅助开发

GitHub Copilot 配置与使用

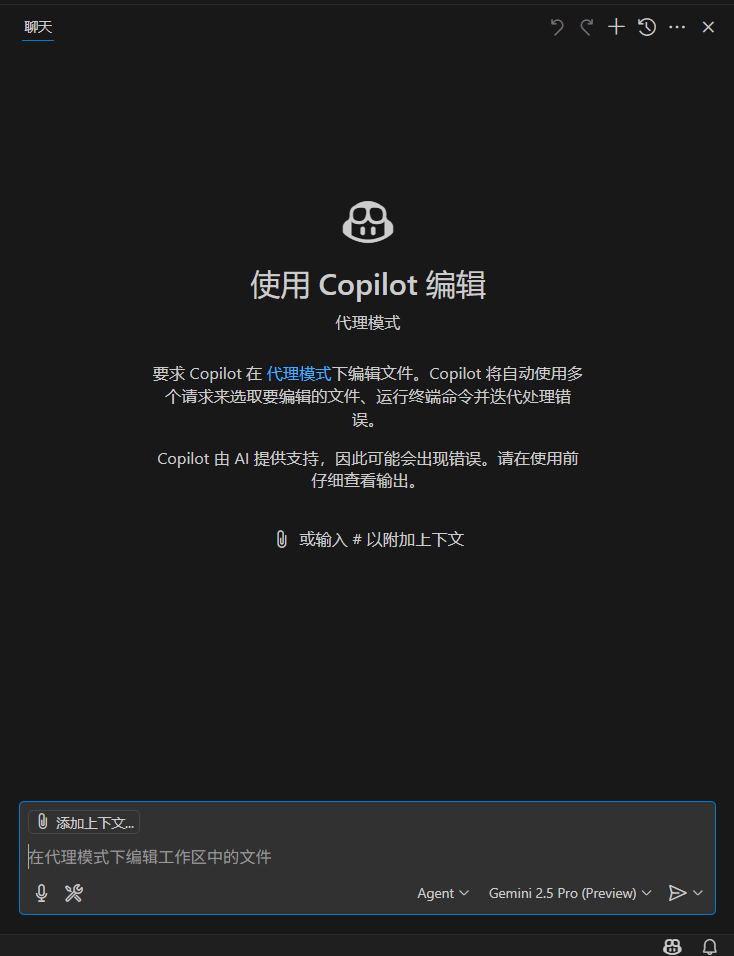

GitHub Copilot 作为 AI 代码助手,能够为 Verilog 开发提供智能化的编程支持。虽然相比传统软件开发,Copilot 在 FPGA 逻辑和时序代码的处理上还有一定局限性,但在以下方面仍能提供显著帮助:

- 自动代码补全:根据上下文智能生成代码片段

- 模块例化:自动生成模块实例化代码和端口连接

- 通用逻辑生成:协助编写计数器、状态机等常见逻辑

- 代码优化建议:提供编码规范和最佳实践建议

使用技巧

- 快速唤起聊天界面:使用快捷键

Shift+Ctrl+I可以快速打开 Copilot 聊天界面 - 上下文提示:在编写代码时,Copilot 会根据当前文件内容和注释提供相关建议

- 免费额度:GitHub Copilot 目前每月提供一定的免费使用额度,足够个人学习和小型项目使用

使用建议:

- 在复杂的时序逻辑设计中,应以人工检查为主,AI 建议为辅

- 充分利用 AI 的模板生成能力,提高重复性工作的效率

- 结合传统的 FPGA 设计验证流程,确保代码的正确性和可综合性

结语

通过本文的介绍,相信你已经能够在 VSCode 中搭建起一个高效的 Verilog 开发环境。从基础的语法高亮和代码检查,到与 Vivado 的无缝集成,再到 AI 辅助编程,这些工具和配置将大大提升你的 FPGA 开发效率。

在实际开发中,建议根据项目需求和个人习惯进行个性化配置。随着 VSCode 插件生态的不断发展和 AI 技术的进步,Verilog 开发体验将会越来越好。记住,工具只是手段,重要的是理解 FPGA 设计的本质和时序要求。